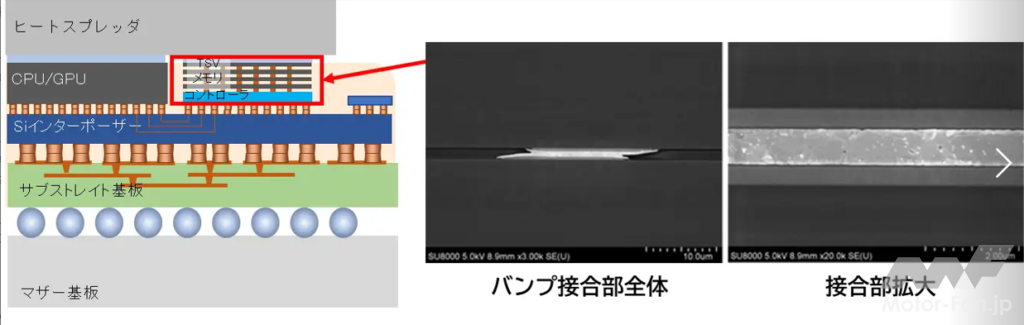

ダイセルと大阪大学産業科学研究所フレキシブル3D実装協働研究所は、半導体の3次元実装に対応した新たな技術開発により、低温(180~250℃)・低加圧(0~0.4 MPa)・短時間(10 分)・直径20 µm・ピッチ150 µmの、半導体のさらなる小型化・高性能化に貢献する銀膜を介した銅マイクロバンプ*1接合を実現した。この接合技術は、新エネルギー・産業技術総合開発機構(NEDO)の先導研究(助成)/先端半導体製造技術(後工程技術)/ポスト5G半導体のための高速通信対応高密度3D実装技術の研究開発で得られた成果である。

ポスト5G、及び6G社会の到来を機に、通信インフラからスマートフォンやタブレット端末といったエッジデバイスまでのあらゆるハードウェアで、膨大な情報を低遅延で高速に伝達する半導体高度化技術への要求が急速に高まっている。その実現には半導体の高集積化に伴う微細化と接続端子の増加が求められ、製造プロセスにおいては前工程での微細化加工だけではなく、後工程で複数の半導体を3次元で集積するパッケージ実装技術の重要度が増している。

半導体チップ間の接続において、現状20~30μmサイズの接続端子には、銅マイクロバンプ接合のためにはんだめっきが使われており、高温・高加圧の厳しいプロセス条件が必要だった。20µm を切るさらなる微細化の実現には、はんだの限界を打ち破り各種特性が期待できる銅の直接接合が必要だ。銅直接接合は、これまでも世界中で研究開発事例が報告されているが、銅の酸化し易さと接合面平滑化の困難さから現実的なプロセスは得られていなかった。

今回開発された技術は、伝統的な銅マイクロバンプ上に銀スパッタ膜を付与し、成長した銀の突起物により、低温、低加圧、及び大気中の条件での短時間接合を実現した。本研究成果により、半導体の3次元実装プロセスの簡素化に大きく貢献し、先端半導体の高性能化・小型化への貢献が期待されている。

*1:銅マイクロバンプ:半導体チップに形成された突起状の微細な銅電極