目次

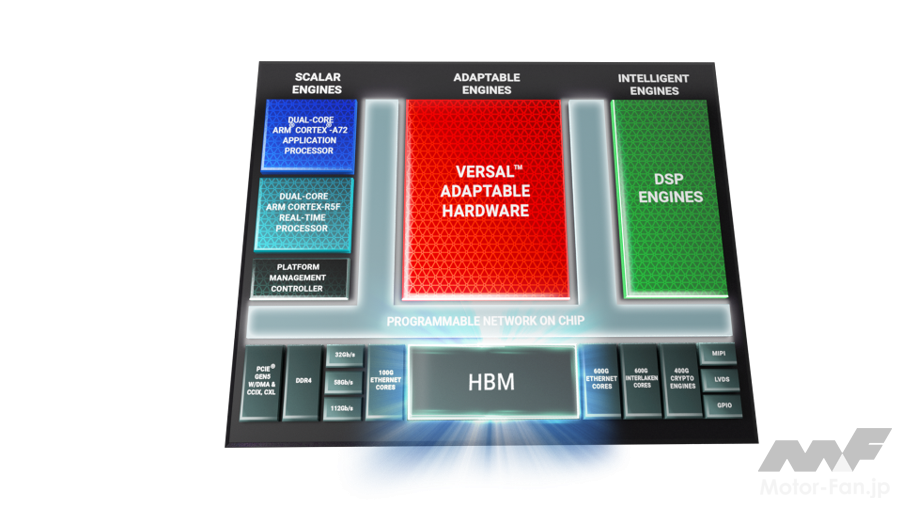

Versal HBMシリーズは、高速なメモリ、セキュアな接続、適応型の演算をひとつのプラットフォームに集約することを可能にする。Versal HBM ACAPには最先端のHBM2e DRAMが内蔵されており、820GB/sのスループットと32GBの容量を提供し、DDR5のインプリメンテーション(注1)と比較してメモリ帯域幅を8倍に向上させ、消費電力を63%削減する。Versal HBMシリーズは、データセンター、有線ネットワーク、テスト/計測、航空宇宙/防衛といった極めて高い演算処理能力を必要とするメモリ バウンド アプリケーションにおけるメモリ需要の高まりに対応するために設計されている。

(注1) DDR5-6400 コンポーネント x 4 から成る標準的システム インプリメンテーションに基づく

ザイリンクスの製品マネージメントおよびマーケティング担当シニア ディレクターであるスーミット・シャー氏(Sumit Shah)は、次のように述べている。

「多くのリアルタイム ハイ パフォーマンス アプリケーションではメモリ帯域幅が致命的なボトルネックとなっており、消費電力と熱の限界値ぎりぎりで動作しています。Versal HBMシリーズは、このようなボトルネックを解消し、パフォーマンスの大幅な向上、システムの消費電力の削減、レイテンシの改善、フォーム ファクターの縮小、データセンター事業者およびネットワーク事業者の総所有コストの削減を可能にするソリューションを提供します」

広い帯域幅、セキュアな接続

Versalプレミアム シリーズをベースに設計されたVersal HBMデバイスには、電力効率に優れたネットワークコアが統合されており、広い帯域幅とセキュアな接続を可能にする。Versal HBMシリーズは、5.6Tb/sのシリアル帯域幅をサポートする112Gb/s PAM4トランシーバー、2.4Tb/sのスケーラブルなイーサネット帯域幅、1.2Tb/sの暗号化されたライン レート スループット、600Gb/sのInterlakenコネクティビティ、CCIXとCXLの両方に対応し 1.5Tb/s帯域幅をサポートするDMA内蔵PCIe Gen5に対応する。これらの多岐にわたるハードIPにより、幅広いプロトコル、データ レート、光学規格に対応するマルチテラビットのネットワークに接続されたコネクティビティが実現し、理想的な消費電力および性能と最短のタイム トゥ マーケットを可能にする。

適応型演算

適応型でヘテロジニアスな演算プラットフォームであるVersal HBMシリーズは、大規模なデータ セットをもつ幅広いワークロードを高速化するために設計されており、低レイテンシのハードウェア並列化用に適応型エンジン、AI推論および信号処理用にDSPエンジン、エンベデッド コンピューティング、プラットフォーム管理、セキュア ブート、コンフィギュレーション用にスカラー エンジンを搭載している。機能が固定されたアクセラレータとは異なり、Versal HBMシリーズはアルゴリズムの進化や新しく登場したプロトコルに合わせてハードウェアを数ミリ秒で動的にリコンフィギュレーションできるため、ハードウェアの再設計や再運用は不要になる。

ネットワークとデータセンターを変革

このような適応型演算および広帯域幅メモリとマルチテラビット接続の融合により、次世代のクラウド アクセラレーションとセキュアなネットワーク接続が現実のものとなる。Versal HBM ACAPは、不正検知、レコメンデーション エンジン、データベース アクセラレーション、データ分析、金融モデリング、自然言語処理(NLP)の深層学習推論などのビッグ データ ワークロードに卓越した性能と電力効率を提供する。最新のサーバー クラス CPU(注2) と比較して実行時間を桁違いに短縮し、4倍のデータ セットをサポートするため、ユーザーは以前よりも大幅に少ない数の低コスト サーバーを使用して大規模なコネクテッド データ セットをもつアプリケーションを展開できるようになる。

(注2) 第 3 世代 Intel Xeon Gold/Platinum スケーラブル プロセッサ

同様に、Versal HBM ACAPは800Gのルーター、スイッチ、セキュリティ アプライアンスにネットワークの拡張性とパフォーマンスを提供する。800Gの次世代ファイアウォールを従来のネッ トワーク プロセッシング ユニット(NPU)でインプリメントする場合、複数のNPUデバイスとDDRモジュールが必要になる。一方、ひとつのVersal HBM ACAPを使用すれば、外部メモリは不要で、劇的に少ない消費電力とはるかに小さいフォーム ファクターで、パケット処理、セキュリティ処理、適応型AIを活用した異常検出を実行できる。顧客が以前より少ないデバイスおよびシステムを使用してアプリケーションを実装できるようになるため、クラウド事業者とネットワーク事業者はCapEx(設備投資)とOpEx(運用コスト)を大きく削減できる。

ハードウェア開発者とソフトウェア開発者の双方が利用可能なプラットフォームであるVersal HBM ACAPには、ハードウェア開発者向けのVivado Design Suite、ソフトウェア開発者向けのVitis統合ソフトウェア プラットフォーム、データ サイエンティスト向けのドメイン特化型フレームワークとアクセラレーション ライブラリを備えた Vitis AIなど、あらゆる開発者に対応するデザイン エントリ ポイントが用意されている。

供給体制

Versal HBMシリーズは、量産実績のある7nm Versalデバイスをベースにして設計されている。そのため、Versalプレミアムシリーズのデバイスおよび評価用ボード上で試作を開始し、Versal HBMシリーズに容易に移行できる。Versal HBMシリーズのサンプル出荷は2022年上半期を予定している。資料は現在提供中で、ツールはアーリーアクセス プログラムを通じて2021年下半期に提供を開始する予定である。

詳細は、ザイリンクスウェブサイトのVersal ACAPとVersal HBMシリーズを参照されたい。